Overview

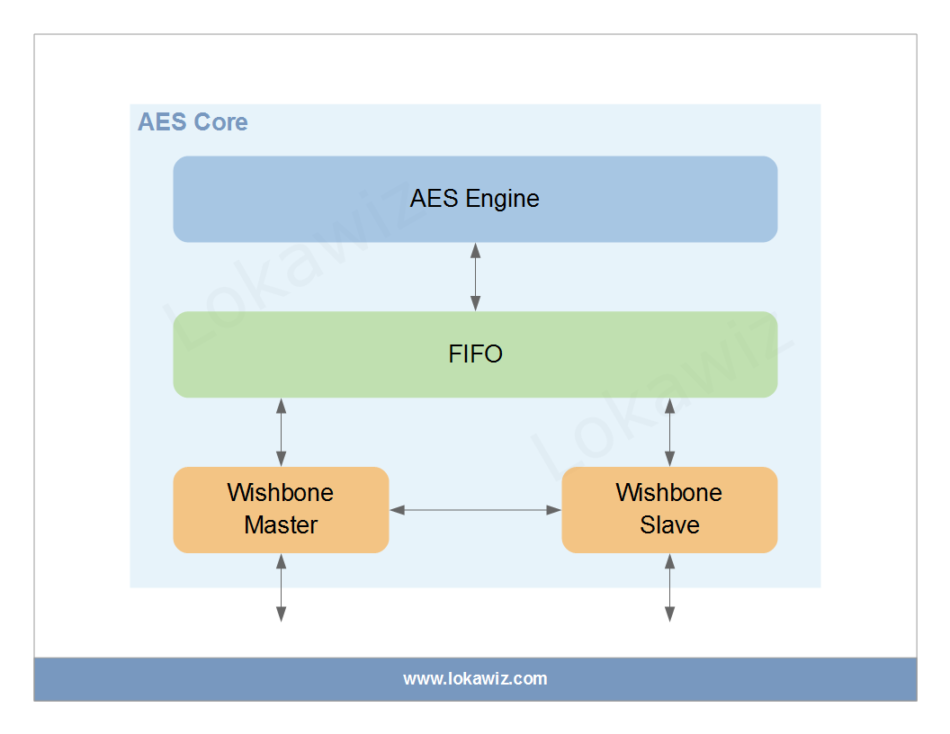

The (Advanced Encryption Standard) AES Core IP from Lokawiz is a wishbone compliant 128-bit AES engine. It has customization options to have multiple configurations, as a wishbone master and slave or a pipeline stage from master to slave. In addition, the core is also optimized for area.

Features of AES Core

- NIST compliant, Rijndael encryption and decryption

- Implements key expansion internally

- Fully synchronous implementation

- Very little area requirement for modern FPGAs

- Wishbone compliant, in multiple configurations

- 128-bit data block and key length AES implementation

- Customization for CBC, OFB, and CTR modes available

Special Feature

- Lesser area requirement than competing cores

- Supports multiple wishbone configurations

- FIFO based, allowing for multiple widths of Wishbone bus

- Customizable FIFO implementations for various FPGA technologies

AES Core Deliverable

The Verilog RTL and standalone simulation test-bench. This is also deliverable as a custom IP to fit into existing system to get instant security.

Target Applications and Platforms

- Applications requiring advanced security for data communication

- Secure data routing

- Secure video surveillance systems

- On-the-fly encryption and decryption of data

- Crypto processors

Why you need this

You are interested in adding security to existing FPGA applications in a modular way especially if you already have a system based on a wishbone bus architecture. Furthermore, this is very useful to you if you also have need for customized secure communications to be added on top of an existing solution.